Apresentado por Marvell

Este artigo faz parte da edição especial da VentureBeat, “IA em Escala: Da Visão à Viabilidade.” Leia mais da edição aqui.

A IA está prestes a enfrentar algumas dores de crescimento sérias.

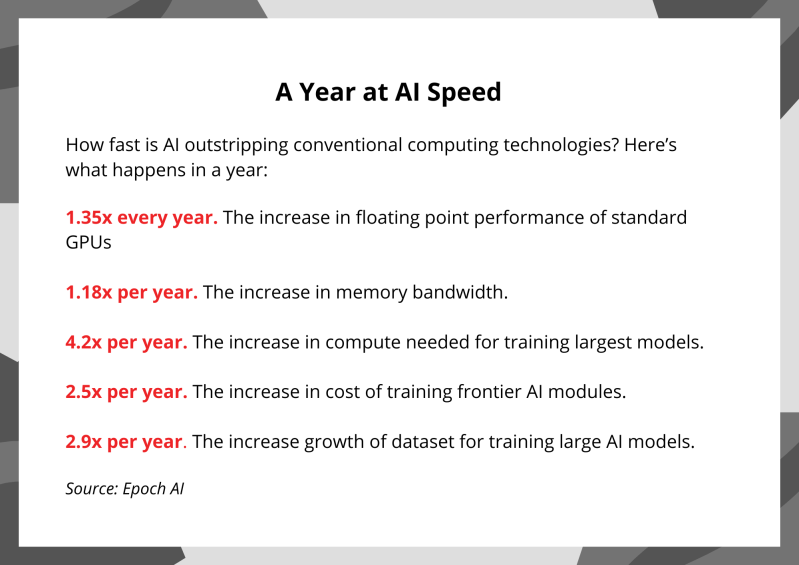

A demanda por serviços de IA está explodindo globalmente. Infelizmente, o desafio de fornecer esses serviços de maneira econômica e sustentável também está crescendo. Previsões indicam que a demanda por energia para IA deve crescer 44,7% anualmente, um aumento que dobrará o consumo de energia dos data centers para 857 terawatts-hora em 2028: Como nação hoje, isso tornaria os data centers o sexto maior consumidor de eletricidade, logo atrás do Japão. É um desequilíbrio que ameaça o mantra “menor, mais barato, mais rápido” que tem guiado cada grande tendência tecnológica nos últimos 50 anos.

Além disso, isso não precisa acontecer. Silício personalizado — silício único otimizado para casos de uso específicos — já está demonstrando como podemos continuar a aumentar o desempenho enquanto reduzimos o consumo de energia, mesmo à medida que a Lei de Moore se aproxima do fim. O silício personalizado pode representar 25% dos aceleradores de IA (XPUs) até 2028 (estimativa da Marvell), e essa é apenas uma categoria de chips que estão se tornando personalizados.

O data center como uma fábrica

A visão de Jensen Huang sobre fábricas de IA é adequada. Estes novos data centers de IA irão operar a um ritmo implacável, 24/7. E, assim como as instalações de fabricação, seu sucesso ou fracasso para os provedores de serviços será determinado pela excelência operacional, a frase de duas palavras que rege a manufatura. Estamos consumindo mais ou menos energia por token do que nossos concorrentes? Por que o tempo médio até a falha está aumentando? Qual é a atual eficácia do equipamento operacional (OEE)? No setor de óleos e químicos, os produtos finais vendidos aos clientes são commodities indistinguíveis. Onde eles diferem é no design do processo, pois aproveitam combinações distintas de tecnologias para extrair ganhos marginais.

O mesmo ocorrerá na IA. A partir de agora, a diversidade será a regra, e os operadores com o menor custo, menor tempo de inatividade e a capacidade de lançar novos serviços e aplicações diferenciadas se tornarão os favoritos de empresas e consumidores.

Em resumo, a melhor infraestrutura vencerá.

O conceito de chip personalizado

Uma das principais formas de diferenciação será através do silício personalizado, possibilitado por semicondutores personalizados — ou seja, chips que contêm IP ou recursos únicos que alcançam desempenho superior para uma aplicação. É um espectro que vai desde aceleradores de IA construídos em torno de um design singular até um chip comercial com IP, núcleos e firmware adicionais para otimizá-lo para um ambiente de software específico. Embora o foco agora esteja principalmente em chips de alto valor, como aceleradores de IA, cada chip será personalizado: a Meta, por exemplo, recentemente revelou um controlador de interface de rede personalizado (NIC), um chip relativamente pouco reconhecido que conecta servidores a redes, para reduzir o impacto do tempo de inatividade.

Uma única pilha de memória de alta largura de banda (HBM) pode exigir uma interface com 2.048 pinos para transferir dados, ou mais de 8.000 por XPU. A personalização pode reduzir drasticamente o consumo de energia, a contagem de pinos e aumentar a capacidade de memória. XPUs com HBM personalizado são esperados em um a dois anos.

A personalização envolverá repensar todos os aspectos do design de semicondutores. Alguns, por exemplo, estão explorando maneiras de otimizar o chip base e as interfaces para gerenciar os gigabytes de memória de alta largura de banda (HBM) usados como cache em aceleradores de IA de alta performance. A otimização pode potencialmente aumentar a memória dentro do pacote do chip em até 33%, reduzir o consumo de energia da interface em 70% e aumentar o espaço disponível de silício para funções lógicas em quase 25% (estimativa da Marvell).

A categoria personalizada também inclui novas classes emergentes de chips de interconexão voltados para ampliar o tamanho e as capacidades dos sistemas de computação. Atualmente, os servidores contêm tipicamente oito ou menos XPUs e/ou CPUs, e todos os componentes estão alojados em uma caixa de alumínio que desliza em um rack. No futuro, os sistemas de IA conterão centenas de aceleradores, além de armazenamento e memória, distribuídos em vários racks conectados com um portfólio de motores ópticos adaptados às especificações de XPUs, controladores CXL, retimers PCIe, processadores de sinal digital ópticos (DSPs) de transmissão-recepção e outros dispositivos.

Muitos desses dispositivos nem existiam há alguns anos, mas espera-se que cresçam rapidamente: 75% dos servidores de IA e nuvem podem conter retimers PCIe em dois anos, de acordo com o The 650 Group. Embora esses dispositivos e servidores estejam ancorados em padrões tecnológicos, as arquiteturas e designs variarão amplamente de nuvem para nuvem.

Uma tabela periódica para semicondutores

Mas como se faz semicondutores personalizados — onde projetar uma plataforma para produzir chips de 3nm ou 2nm pode custar mais de $500 milhões? Em um mercado onde modelos de linguagem grandes (LLMs) mudam a cada poucos meses? E como essas tecnologias funcionarão com ideias emergentes como resfriamento por placa fria ou resfriamento imersivo?

Por mais básico que pareça, tudo começa com os ingredientes elementares. Circuitos serializador-desarializador (SerDes) são a tecnologia “mais importante do mundo” que você nunca ouviu falar. Esses componentes controlam o fluxo de dados entre chips e dispositivos de infraestrutura, como switches e servidores. Um módulo óptico de 800G, por exemplo, é feito com oito SerDes de 100G. Um único rack de data center conterá dezenas de milhares de SerDes. Você pode pensar neles como as moléculas de redes: blocos de construção fundamentais que têm uma influência desproporcional na saúde do sistema como um todo. Reduzir levemente os picojoules consumidos na transmissão de bits por meio de um SerDes pode se traduzir em economias substanciais de energia em uma infraestrutura global.

Da mesma forma, a embalagem de chips agora desempenha um papel crucial no design dos chips, pois fornece um mecanismo para otimizar a entrega de energia e os caminhos de dados enquanto continua a melhorar o desempenho computacional. Mais de 50% da energia em um chip pode ser consumida ao mover dados entre diferentes subsistemas dentro do próprio chip.

Indústria de chips 2.0?

À medida que o personalizado se torna a norma, também enfrentaremos um novo dilema: como uma empresa pode entregar produtos personalizados e ainda aproveitar os benefícios da fabricação em massa? Até agora, os fabricantes de semicondutores tiveram sucesso fabricando grandes quantidades de um pequeno número de dispositivos. “Personalizado” costumava significar fazer ações bastante simples, como ajustar a velocidade ou o tamanho do cache, semelhante a como um varejista poderia oferecer o mesmo suéter básico em algumas novas cores.

O primeiro passo — e já estamos vendo isso — virá quando houver uma definição melhor dos serviços envolvidos no desenvolvimento de semicondutores personalizados. Alguns provavelmente se concentrarão mais no design de chips e IP. No outro extremo do espectro, você verá empresas oferecendo serviços de abastecimento e fabricação. Outras ainda podem se concentrar em dispositivos e categorias específicas. Apenas algumas poucas empresas selecionadas fornecerão o portfólio completo de serviços. A própria IA também desempenhará um papel, reduzindo o tempo e o custo necessários para tarefas de design de meses para, em muitos casos, minutos. Isso, por sua vez, abrirá as portas para mais clientes e mais classes de chips.

O setor terá sucesso? Claro. Não é a primeira vez que somos desafiados a fazer o impossível.

Raghib Hussain é Presidente, Produtos e Tecnologias na Marvell.

1. IDC. Set 2024.

2. Statista.

3. Estimativas da Marvell baseadas em relatórios de analistas e previsões internas.

4. Estimativa interna da Marvell.

5. Grupo 650 Mai 2024.

6. IBM

7. Gráfico: Epoch AI, Jun 2024.

Este artigo contém declarações prospectivas dentro do significado das leis federais de valores mobiliários que envolvem riscos e incertezas. Declarações prospectivas incluem, sem limitação, qualquer declaração que possa prever, prever, indicar ou implicar eventos ou realizações futuras. Os eventos ou resultados reais podem diferir materialmente dos contemplados neste blog. Declarações prospectivas são apenas previsões e estão sujeitas a riscos, incertezas e suposições que são difíceis de prever, incluindo aqueles descritos na seção “Fatores de Risco” de nossos Relatórios Anuais no Formulário 10-K, Relatórios Trimestrais no Formulário 10-Q e outros documentos que arquivamos ocasionalmente junto à SEC. Declarações prospectivas falam apenas na data em que são feitas. Os leitores são aconselhados a não confiar excessivamente em declarações prospectivas, e nenhuma pessoa assume qualquer obrigação de atualizar ou revisar tais declarações prospectivas, seja como resultado de novas informações, eventos futuros ou de outra forma.

Artigos patrocinados são conteúdos produzidos por uma empresa que está pagando pelo post ou tem um relacionamento comercial com a VentureBeat, e são sempre claramente marcados. Para mais informações, entre em contato com

Conteúdo relacionado

OpenAI está supostamente em negociações para comprar a Windsurf por $3 bilhões, com novidades esperadas para esta semana.

[the_ad id="145565"] A Windsurf, fabricante de um popular assistente de codificação por IA, está em negociações para ser adquirida pela OpenAI por cerca de $3 bilhões, segundo…

A OpenAI procurou o criador do Cursor antes de iniciar negociações para comprar a Windsurf por $3 bilhões.

[the_ad id="145565"] Quando a notícia de que a OpenAI estava em negociações para adquirir a empresa de codificação AI Windsurf por $3 bilhões surgiu, uma das primeiras…

Como a IA está redesenhando os mapas de eletricidade do mundo: Insights do Relatório da AIE

[the_ad id="145565"] A inteligência artificial (IA) não está apenas transformando a tecnologia; ela também está mudando de forma significativa o setor energético global. De…